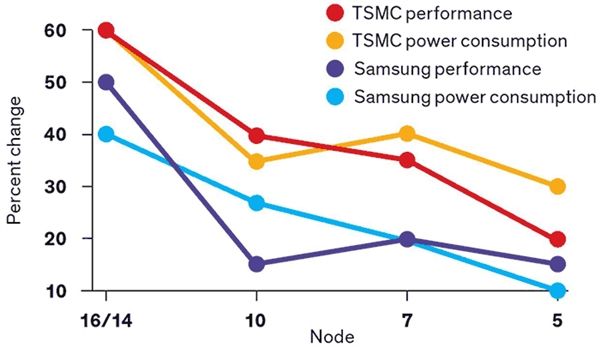

这几年,虽然摩尔定律基本失效或者说越来越迟缓,但是在半导体工艺上,几大巨头却是杀得兴起。Intel终于进入10nm工艺时代并将在后年转入7nm,台积电、三星则纷纷完成了7nm工艺的布局并奔向5nm、3nm。

现在, 台积电又官方宣布,正式启动2nm工艺的研发,工厂设置在位于台湾新竹的南方科技园,预计2024年投入生产 ,时间节奏上还是相当的快。

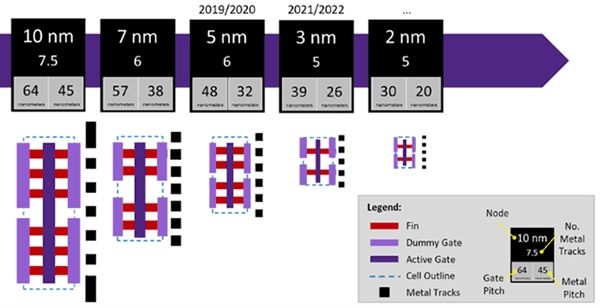

按照台积电给出的指标,2nm工艺是一个重要节点,Metal Track(金属单元高度)和3nm一样维持在5x,同时 Gate Pitch(晶体管栅极间距)缩小到30nm,Metal Pitch(金属间距)缩小到20nm,相比于3nm都小了23%。

台积电没有透露2nm工艺所需要的技术和材料,看晶体管结构示意图和目前并没有明显变化,能在硅半导体工艺上继续压榨到如此地步真是堪称奇迹,接下来就看能不能做到1nm了。

当然,在那之前,台积电还要接连经历7nm+、6nm、5nm、3nm等多个工艺节点。

其中, 7nm+首次引入EUV极紫外光刻技术,目前已经投入量产;6nm只是7nm的一个升级版,明年第一季度试产;5nm全面导入极紫外光刻,已经开始风险性试产,明年底之前量产,苹果A14、AMD五代锐龙(Zen 4都有望采纳);3nm有望在2021年试产、2022年量产。

三星也早就规划到了3nm,预期2021年量产。